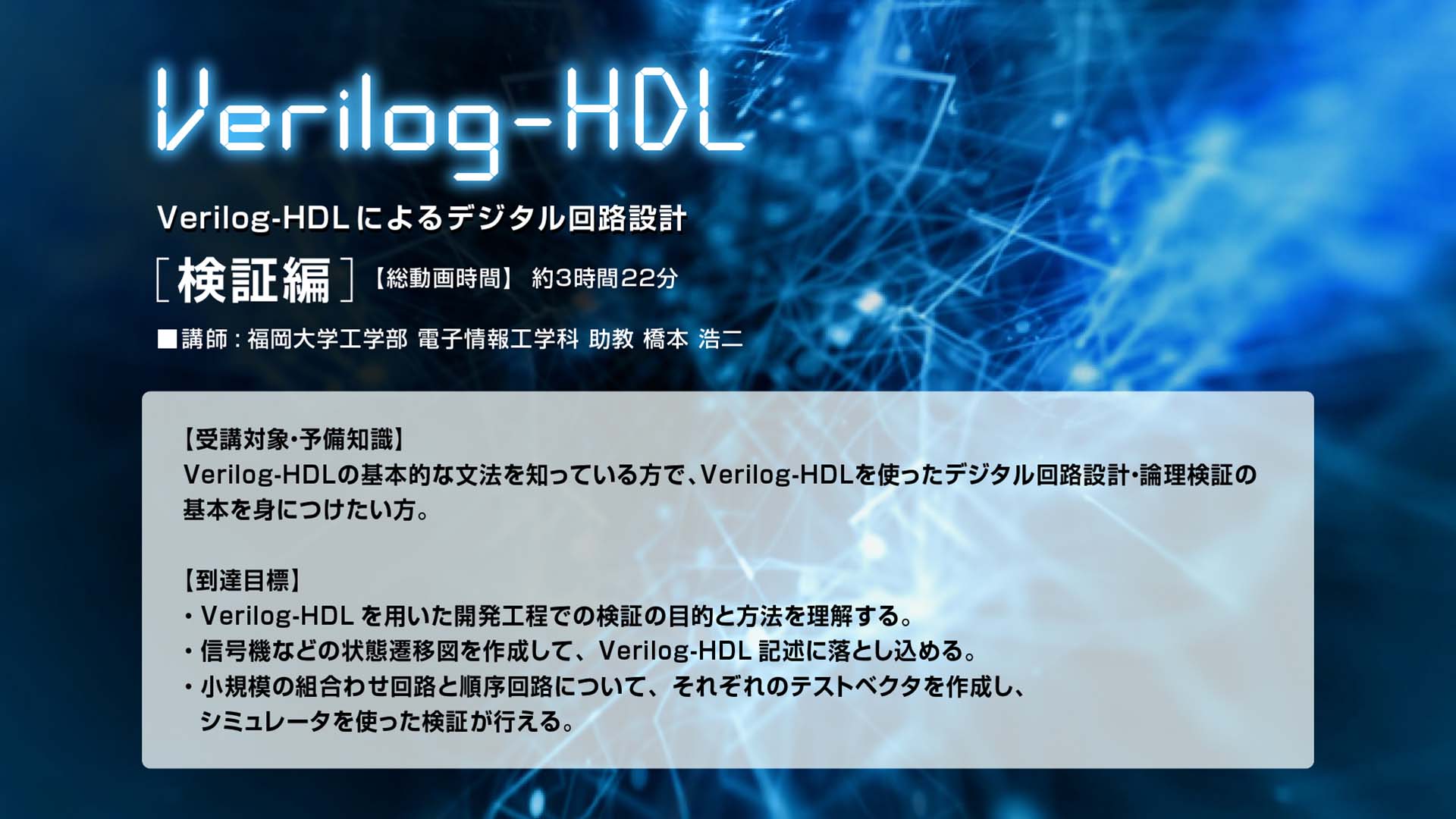

Verilog-HDLによるデジタル回路設計(検証編)

【講師】福岡大学 工学部 電子情報工学科 助教 橋本 浩二

【受講料】16,500円(税込)

信号機や自動販売機をモデルとした例題で示される仕様をVerilog-HDLを使って実現し、さらにその記述が仕様通りの動作をしているかどうかを検証する手法を学習する演習中心の講座です。講師によるシミュレータの操作を視聴することで学びます。

※講座テキストは、「関連ファイルダウンロード」からダウンロードできます(閲覧用パスワード付きPDFファイル)。

パスワードは、同じ場所に掲載の“パスワード.pdf”をご確認ください。

なお、ダウンロードした講座テキスト等を第三者に提供、また閲覧させることは禁じられています。

このセットの最終動画を最後まで視聴すると[受験する]ボタンが表示されます。受験の上、合格すると修了証をダウンロードできます。

【総動画時間】

約3時間22分

【受講対象・予備知識】

Verilog-HDLの基本的な文法を知っている方で、Verilog-HDLを使ったデジタル回路設計・論理検証の基本を身につけたい方。

【到達目標】

・Verilog-HDLを用いた開発工程での検証の目的と方法を理解する。

・信号機などの状態遷移図を作成して、Verilog-HDL記述に落とし込める。

・小規模の組合わせ回路と順序回路について、それぞれのテストベクタを作成し、シミュレータを使った検証が行える。

【学習環境】

・テキスト

【講師の環境】

・PC

Verilogシミュレータ: ModelSim-Altera

【目次】

1章 Verilog-HDLによる論理回路の設計

1.LSIの開発フロー

2.論理回路の設計手順

【例題1章-1】自動販売機制御回路

【例題1章-2】信号機制御回路

2章 Verilog-HDLによる論理検証

1.論理検証とは

2.組合せ回路の論理検証

3.順序回路の論理検証

4.シミュレータによる検証

5.例題による解説

【演習2章-1】自動販売機制御回路

【演習2章-2】信号機制御回路

【ステップアップ1】自動販売機の拡張(1)

【ステップアップ2】自動販売機の拡張(2)

【ステップアップ3】信号機の拡張(1)

【ステップアップ4】信号機の拡張(2)

【ステップアップ5】信号機の拡張(3)

※「ステップアップ2、4、5」の解答の解説は省略。

テキストの解答サンプルを参照いただきます。

※すべての動画視聴後にアンケートが表示されますので、回答へのご協力をお願いいたします。

アンケートは以下からでもご回答いただけます。

※銀行振込のみ複数の講座の一括購入が可能です。

視聴期限は購入後180日間です。

購入済の方は、ログインすると視聴できます関連ファイルダウンロード

※関連ファイルは動画視聴可能になるとダウンロードできます

- text_Verilog-HDLによるデジタル回路設計(検証).pdf(590.84 KB)

- 補助資料①_MentorGraphics ModelSim BL2受講者用操作マニュアルrev2_2_20250220.pdf(1.14 MB)

- パスワード.pdf(247.75 KB)

コメント

ログイン、もしくは会員登録いただくと、コメントできます。